# Application Manual

# Programmable Voltage Controlled Oscillator

# VG7050ECN

**SEIKO EPSON CORPORATION**

#### **NOTICE**

- This material is subject to change without notice.

- Any part of this material may not be reproduced or duplicated in any form or any means without the written permission of Seiko Epson.

- The information about applied circuitry, software, usage, etc. written in this material is intended for reference only. Seiko Epson does not assume any liability for the occurrence of infringing on any patent or copyright of a third party. This material does not authorize the licensing for any patent or intellectual copyrights.

- When exporting the products or technology described in this material, you should comply with the

applicable export control laws and regulations and follow the procedures required by such laws and

regulations.

- You are requested not to use the products (and any technical information furnished, if any) for the

development and/or manufacture of weapon of mass destruction or for other military purposes. You

are also requested that you would not make the products available to any third party who may use

the products for such prohibited purposes.

- These products are intended for general use in electronic equipment. When using them in specific applications that require extremely high reliability, such as the applications stated below, you must obtain permission from Seiko Epson in advance.

- Space equipment (artificial satellites, rockets, etc.) / Transportation vehicles and related (automobiles, aircraft, trains, vessels, etc.) / Medical instruments to sustain life / Submarine transmitters / Power stations and related / Fire work equipment and security equipment / traffic control equipment / and others requiring equivalent reliability.

- All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective.

# **Table of Contents**

| 1. | O            | verview                                                        | 1    |

|----|--------------|----------------------------------------------------------------|------|

| 2. | Pa           | art Number                                                     | 2    |

| 3. | В            | lock Diagram                                                   | 3    |

| 4. | Pi           | n Assignments                                                  | 4    |

|    | 4.1.         | Pin Assignments                                                |      |

|    | 4.2.         | Pin Descriptions                                               | 4    |

| 5. | FI           | ectrical Characteristics                                       | 5    |

|    | <br>5.1.     | Absolute Maximum Ratings                                       |      |

|    | 5.2.         | DC Characteristics                                             |      |

|    | 5.3.         | AC Characteristics                                             | 7    |

|    | 5.4.         | VCXO Control Voltage Input (V <sub>C</sub> )                   | . 11 |

|    | 5.5.         | LVPECL                                                         | .12  |

|    | 5.6.         | Startup                                                        | .14  |

| 6. | Fι           | unctions                                                       | 15   |

|    | 6.1.         | Overview                                                       | .15  |

|    | 6.2.         | Setting of the Kv                                              | .15  |

|    | 6.3.         | Setting of the Output Frequency                                |      |

|    |              | 3.1. Calculation of the Frequency Setting                      |      |

|    |              | 3.2. Reconfiguring Frequency Setting                           |      |

|    |              | 4.1. Connection of I <sup>2</sup> C Bus                        | .20  |

|    | 6.4          | 4.2. I <sup>2</sup> C Bus Protocols Supported by the VG7050ECN | .21  |

|    | _            | 4.3. START Condition and STOP Condition                        |      |

|    |              | 4.4. Byte Format and ACK/NACK                                  |      |

| 7  |              | egisters                                                       |      |

|    | 7.1.         | List of Registers                                              |      |

|    | 7.1.<br>7.2. | Product Code 0 Register                                        |      |

|    | 7.2.<br>7.3. | Product Code 1 Register                                        |      |

|    | 7.3.<br>7.4. | Revision Code Register                                         |      |

|    | 7.5.         | ID Code 0 Register                                             |      |

|    | 7.6.         | ID Code 1 Register                                             |      |

|    | 7.7.         | ODIV Register                                                  |      |

|    | 7.8.         | NINT Register                                                  | . 26 |

|    | 7.9.         | NFRAC Register                                                 |      |

|    | 7.10.        | PLL Control Register                                           | . 27 |

|    | 7.11.        | FSEL Status Register                                           | .28  |

|    | 7.12.        | KV Register                                                    | .28  |

| 8. | Di           | imensions                                                      | 29   |

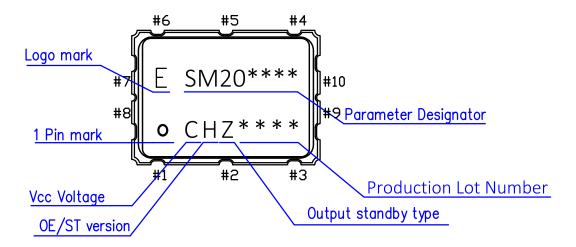

| 9. | D            | evice Marking                                                  | 30   |

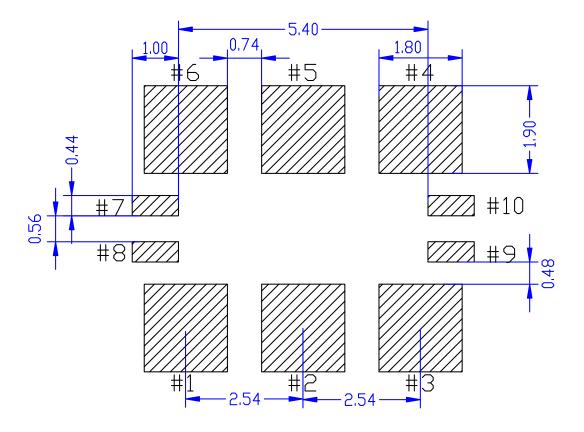

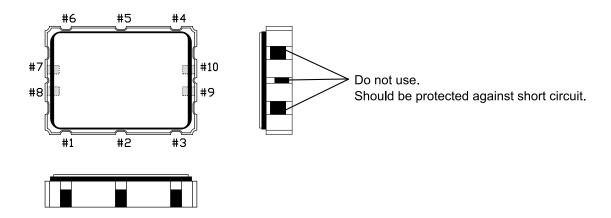

| 10 |              | oldering Pattern                                               |      |

|    |              | <del>-</del>                                                   |      |

| VG7050ECN            | <b>EPSON</b> |

|----------------------|--------------|

| 11. Application Note | 32           |

#### 1. Overview

Programmable Voltage Controlled Oscillator: VG7050ECN is a low jitter programmable VCXO at any frequency. VG7050ECN consists of VCXO, PLL and LVPECL output buffer. Its output frequency is programmable from 50 MHz to 800 MHz with almost 2 ppb resolution.

VCXO supplies stable reference clock to PLL with fundamental tone crystal. Kv of VCXO can be programmed via I<sup>2</sup>C interface.

PLL consists of a low jitter fractional-N PLL technology. The components for loop filter are embedded into IC, so no external component is needed.

- Programmable clock output frequency from 50 MHz to 800 MHz

- Frequency setting resolution is around 2 ppb

- Kv is programmable

- · Low jitter and high reliability clock source from the fundamental tone internal crystal

- · Low jitter and low noise PLL

- Four power-up default frequency

- Factory preset device options

- OE polarity

- Output standby type: Hi-Z or OUT = "L", OUTN = "H"

- I<sup>2</sup>C interface slave address

- Embedded resistors and capacitors for oscillator and loop filter for PLL

- I<sup>2</sup>C interface

- LVPECL output

- 10-pin ceramic 5 x 7 mm package

- 2.5 V or 3.3 V supply voltage modes

- -40 °C ~ +85 °C ambient operating temperature

- Pb-free / RoHS-compliant

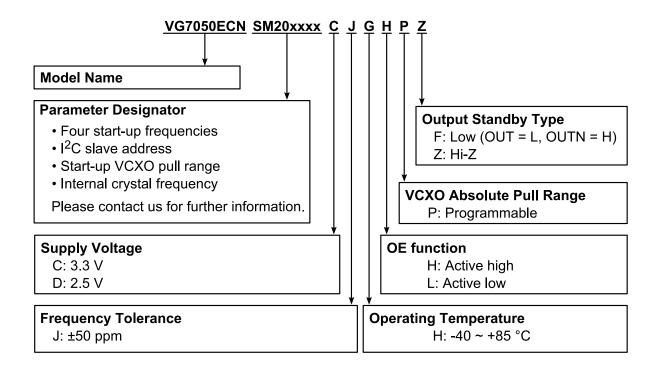

## 2. Part Number

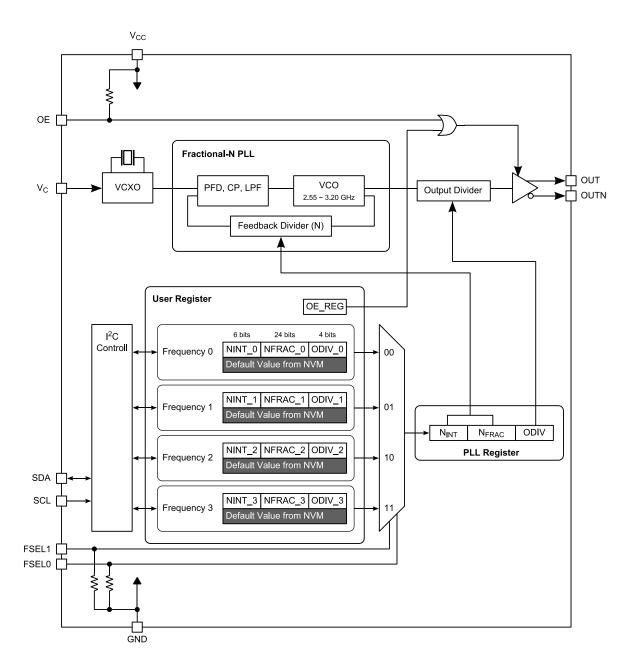

# 3. Block Diagram

\* If OE pin is configured as active low, OE pin is pulled down to GND with internal pull down resistor.

Figure 3.1. VG7050ECN Block Diagram

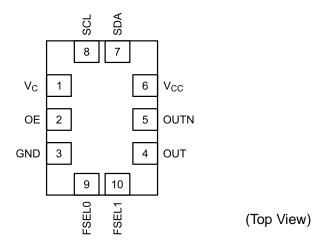

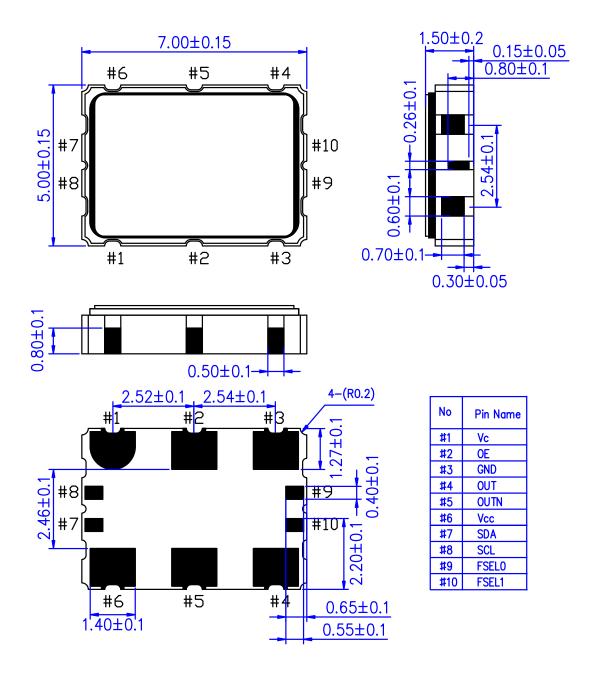

# 4. Pin Assignments

# 4.1. Pin Assignments

# 4.2. Pin Descriptions

**Table 4.1 Pin Descriptions**

| No. | Pin Name                 | Туре                                | )         | Function                                                                                          |  |  |  |  |  |

|-----|--------------------------|-------------------------------------|-----------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1   | V <sub>C</sub>           | Input                               | -         | VCXO Control Voltage Input                                                                        |  |  |  |  |  |

| 2   | OE                       | Input                               | Pull-up/  | Output Enable (Active High)                                                                       |  |  |  |  |  |

|     |                          |                                     |           | OE Input  "H" or Open  Outputs are enabled.  "L"  High-impedance state  or  OUT = "L", OUTN = "H" |  |  |  |  |  |

|     |                          |                                     | Pull-down | Output Enable (Active Low)                                                                        |  |  |  |  |  |

|     |                          |                                     |           | OE Input OUT, OUTN pin status                                                                     |  |  |  |  |  |

|     |                          |                                     |           | "H" High-impedance state                                                                          |  |  |  |  |  |

|     |                          |                                     |           | or<br>OUT = "L", OUTN = "H"                                                                       |  |  |  |  |  |

|     |                          |                                     |           | "L" or Open Outputs are enabled.                                                                  |  |  |  |  |  |

| 3   | GND                      | Power                               | -         | Negative Power Supply                                                                             |  |  |  |  |  |

| 4   | OUT                      | Output                              | -         | Differential clock output. LVPECL interface levels.                                               |  |  |  |  |  |

| 5   | OUTN                     | Output                              | -         |                                                                                                   |  |  |  |  |  |

| 6   | V <sub>CC</sub>          | Power                               | -         | Positive Power Supply                                                                             |  |  |  |  |  |

| 7   | SDA <sup>*1</sup>        | Input/Output                        | -         | I <sup>2</sup> C Data Input/Output<br>Input: LVCMOS interface levels,<br>Output: Open drain       |  |  |  |  |  |

| 8   | SCL*1                    | Input                               | -         | I <sup>2</sup> C Clock Input                                                                      |  |  |  |  |  |

| 9   | FSEL0                    | Input                               | Pull-down | Frequency select                                                                                  |  |  |  |  |  |

| 10  | 10 FSEL1 Input Pull-down |                                     |           |                                                                                                   |  |  |  |  |  |

|     |                          | Pull-down" refersull-up resistor to |           | CN internal input resistors.<br>sary.                                                             |  |  |  |  |  |

## 5. Electrical Characteristics

## 5.1. Absolute Maximum Ratings

| Item                            | Symbol           | Condition                                      | Min.      | Тур. | Max.                  | Units |

|---------------------------------|------------------|------------------------------------------------|-----------|------|-----------------------|-------|

| Supply voltage, V <sub>CC</sub> | Vcc              | GND = 0 V                                      | -0.3      | -    | 4.0                   | V     |

| Pull-up voltage                 | $V_{PU}$         | SDA, SCL                                       | -0.3      | -    | 4.0                   | V     |

| Input voltage 1                 | V <sub>in1</sub> | GND = 0 V,<br>Input pins except to SDA and SCL | GND - 0.3 | -    | V <sub>CC</sub> + 0.3 | ٧     |

| Input voltage 2                 | V <sub>in2</sub> | GND = 0 V, SDA, SCL                            | GND - 0.3 | -    | 4.0                   | V     |

| Storage temperature             | Tstg             | Store as bare product                          | -55       | -    | +125                  | °C    |

| ESD sensitivity                 | ESD              | НВМ                                            | 2000      | -    | -                     | V     |

|                                 |                  | MM                                             | 200       | -    | -                     |       |

Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

These are stress ratings only. Functional operation of the device at these or any other conditions beyond those listed in the "DC characteristics" or "AC characteristics" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 5.2. DC Characteristics

Table 5.1. Power Supply, Operating Temperature

GND = 0 V, Ta = -40 ~ +85 °C

| Item                                  | Symbol          | Conditions                              | Min.                                 | Тур.                 | Max.  | Units |

|---------------------------------------|-----------------|-----------------------------------------|--------------------------------------|----------------------|-------|-------|

| Positive supply voltage               | Vcc             | 3.3 V option                            | 2.970                                | 3.3                  | 3.630 | V     |

|                                       |                 | 2.5 V option                            | 2.375                                | 2.5                  | 2.625 |       |

| Positive supply current <sup>*1</sup> | I <sub>CC</sub> | OE = Enable, Outputs terminated with    | th 50 $\Omega$ to $V_{C}$            | <sub>C</sub> – 2.0 V |       |       |

| Output enable mode                    |                 | 3.3 V option                            | -                                    | •                    | 90    | mA    |

|                                       |                 | 2.5 V option                            | -                                    | •                    | 90    |       |

| Positive supply current *1            | I_dis           | OE = Disable, Output standby type: I    | Hi-Z                                 |                      |       |       |

| Output disable mode                   |                 | 3.3 V option                            | -                                    | •                    | 40    | mA    |

|                                       |                 | 2.5 V option                            | -                                    | •                    | 40    |       |

|                                       |                 |                                         | OE = Disable, Output standby type: I | H")                  |       |       |

|                                       |                 | 3.3 V option                            | -                                    | •                    | 70    | mA    |

|                                       |                 | 2.5 V option                            | -                                    | •                    | 70    |       |

| Operating temperature                 | Та              | -                                       | -40                                  | -                    | +85   | °C    |

| Note 1: Guaranteed by des             | sign, chara     | cterization, and/or simulation only and | d not producti                       | on tested.           |       |       |

# Table 5.2. Logic I/O

$V_{CC}$  = 3.3 V ± 10% or 2.5 V ± 5%, GND = 0 V, Ta = -40 ~ +85 °C

| Item                            | Symbol            | Conditions                                             | Min.                  | Тур.       | Max.                  | Units |

|---------------------------------|-------------------|--------------------------------------------------------|-----------------------|------------|-----------------------|-------|

| Pull-up voltage                 | V <sub>PU</sub>   | SDA, SCL                                               | V <sub>CC</sub> x 0.7 | -          | 3.630                 | V     |

| High level input voltage 1      | V <sub>IH1</sub>  | OE, FSEL0, FSEL1                                       | V <sub>CC</sub> x 0.7 | -          | V <sub>CC</sub> + 0.3 | V     |

| High level input voltage 2      | V <sub>IH2</sub>  | SDA, SCL, Pull Up Voltage = V <sub>PU</sub>            | V <sub>CC</sub> x 0.7 | -          | 3.630                 | V     |

| Low level input voltage         | V <sub>IL</sub>   | SDA, SCL, OE, FSEL0, FSEL1                             | -0.3                  | -          | V <sub>CC</sub> x 0.3 | V     |

| High level input current 1      | I <sub>IH1</sub>  | SDA, SCL, OE (Active High) , FSEL0, FSEL1              | -                     | -          | 2                     | μΑ    |

| High level input current 2      | I <sub>IH2</sub>  | V <sub>CC</sub> = 3.3 V ± 10%,<br>OE (Active Low)      | -                     | -          | 170                   | μΑ    |

|                                 |                   | V <sub>CC</sub> = 2.5 V ± 5%,<br>OE (Active Low)       | -                     | -          | 100                   |       |

| Low level input current 1       | I <sub>IL1</sub>  | SDA, SCL, OE (Active Low),<br>FSEL0, FSEL1             | -2                    | -          | -                     | μA    |

| Low level input current 2       | I <sub>IL2</sub>  | $V_{CC} = 3.3 \text{ V} \pm 10\%,$<br>OE (Active High) | -70                   | -          | -                     | μΑ    |

|                                 |                   | $V_{CC} = 2.5 \text{ V} \pm 5\%,$<br>OE (Active High)  | -35                   | -          | -                     |       |

| Low level output voltage        | V <sub>OL</sub>   | SDA, at 3 mA sink current                              | 0                     | -          | 0.4                   | V     |

| Low level output current        | I <sub>OL</sub>   | SDA, V <sub>OL</sub> = 0.4 V                           | 3                     | -          | -                     | mA    |

| Pull-up resistor                | R <sub>UP</sub>   | OE (Active High)                                       | -                     | 85         | -                     | kΩ    |

|                                 | R <sub>DOWN</sub> | OE (Active Low), FSEL0, FSEL1                          | -                     | 35         | -                     |       |

| Input Capacitance <sup>*1</sup> | C <sub>IN</sub>   | OE, SDA, SCL, FSEL0, FSEL1                             | -                     | 5          | -                     | pF    |

| Note 1: Guaranteed by desi      | gn, charact       | erization, and/or simulation only and                  | d not production      | on tested. |                       |       |

VG7050ECN

#### 5.3. AC Characteristics

**Table 5.3. Output Frequency Characteristics**

$V_{CC} = 3.3 \text{ V} \pm 10\% \text{ or } 2.5 \text{ V} \pm 5\%, \text{ GND} = 0 \text{ V}, \text{ Ta} = -40 \sim +85 ^{\circ}\text{C}$

|                                                             | • 00              |           | 0.0 1 - 1070                                                                              | · ·                              | o, o          | <b>0</b> 1, 10 | . •  |                  |

|-------------------------------------------------------------|-------------------|-----------|-------------------------------------------------------------------------------------------|----------------------------------|---------------|----------------|------|------------------|

| Item                                                        | Symbol            |           | Condit                                                                                    | ions                             | Min.          | Тур.           | Max. | Units            |

| Output frequency                                            | f <sub>O</sub>    | Οl        | JT, OUTN                                                                                  |                                  | 50            | -              | 800  | MHz              |

| Internal crystal frequency                                  | f <sub>XTAL</sub> |           | -                                                                                         |                                  | -             | 114.144        | -    | MHz              |

| Frequency reprogramming resolution                          | M <sub>RES</sub>  |           | -                                                                                         |                                  | 2.2           | -              | 2.8  | ppb              |

| Frequency tolerance 1                                       | f_tol             | fre<br>su | is parameter inc<br>equency tolerand<br>pply voltage vari<br>ars aging <sup>2</sup> at 25 | e, temperature,<br>iation and 10 | -50           | -              | +50  | 10 <sup>-6</sup> |

| Delta frequency for continuous output 1                     | -                 |           | om Center Freque                                                                          | uency that is<br>NEW_FREQ bit    | -500          | -              | +500 | 10 <sup>-6</sup> |

| Setting time for large frequency change                     | t <sub>SET1</sub> |           | om setting NEW tput new frequer                                                           |                                  | -             | ı              | 1.5  | ms               |

| Setting time after<br>FSEL0 and FSEL1 values<br>are changed | t <sub>SET2</sub> |           | -                                                                                         | -                                | -             | 1.5            | ms   |                  |

| Setting time for small frequency change *1                  | t <sub>SET3</sub> | fre       | ±500 ppm from o<br>equency that is d<br>tting NEW_FRE                                     | efined by                        | -             | ı              | 100  | μs               |

| SSB phase noise*1                                           | F <sub>CN</sub>   | fo        | = 622.08 MHz, f                                                                           | rom carrier                      |               |                |      |                  |

|                                                             |                   |           | $V_{CC} = 3.3 \text{ V}^{*3}$                                                             | 100 Hz                           | -             | -75.7          | -    | dBc/Hz           |

|                                                             |                   |           |                                                                                           | 1 kHz                            | -             | -101.6         | -    |                  |

|                                                             |                   |           |                                                                                           | 10 kHz                           | -             | -118.8         | -    |                  |

|                                                             |                   |           |                                                                                           | 100 kHz                          | -             | -121.3         | -    |                  |

|                                                             |                   |           |                                                                                           | 1 MHz                            | -             | -129.3         | -    |                  |

|                                                             |                   |           |                                                                                           | 10 MHz                           | -             | -146.8         | -    |                  |

|                                                             |                   |           | $V_{CC} = 2.5 \text{ V}^{^{4}}$                                                           | 100 Hz                           | -             | -72.7          | -    |                  |

|                                                             |                   |           |                                                                                           | 1 kHz                            | -             | -99.3          | -    |                  |

|                                                             |                   |           |                                                                                           | 10 kHz                           | -             | -118.2         | -    |                  |

|                                                             |                   |           |                                                                                           | 100 kHz                          | -             | -121.3         | -    |                  |

|                                                             |                   |           |                                                                                           | 1 MHz                            | -             | -129.2         | -    |                  |

|                                                             |                   |           |                                                                                           | 10 MHz                           | -             | -146.9         | -    |                  |

| RMS phase jitter 1, 4                                       | t <sub>PJ</sub>   | $f_{O}$   |                                                                                           | ntegration range                 |               | MHz (OC-4      | -8)  |                  |

|                                                             |                   |           | $V_{CC} = 3.3 \text{ V}^{3}$                                                              |                                  | -             | 0.3            | -    | ps               |

|                                                             |                   |           | $V_{CC} = 2.5 \text{ V}^{^{^{4}}}$                                                        |                                  | -             | 0.3            | -    | ps               |

|                                                             |                   | $f_{O}$   | = 622.08 MHz, I                                                                           | ntegration range                 | : 20 kHz – 50 | ) MHz          |      |                  |

|                                                             |                   |           | $V_{CC} = 3.3 \text{ V}^{3}$                                                              |                                  | -             | 0.3            | -    | ps               |

|                                                             |                   |           | $V_{CC} = 2.5 \text{ V}^{^{-4}}$                                                          |                                  | -             | 0.3            | -    | ps               |

|                                                             |                   | $f_{O}$   | = 622.08 MHz, I                                                                           | ntegration range                 | : 50 kHz – 80 | MHz (OC-1      | 92)  |                  |

|                                                             |                   |           | $V_{CC} = 3.3 \text{ V}^{*3}$                                                             |                                  | -             | 0.3            | -    | ps               |

|                                                             |                   |           | $V_{CC} = 2.5 \text{ V}^{-4}$                                                             |                                  | -             | 0.3            | -    | ps               |

|                                                             |                   |           |                                                                                           |                                  |               |                |      |                  |

Note 1: Guaranteed by design, characterization, and/or simulation only and not production tested.

Note 2: The aging in the frequency tolerance is from environmental tests results to the expectation of the amount of the frequency variation. This doesn't guarantee the product life cycle.

Note 3: f<sub>XTAL</sub> = 114.144 MHz, Ta = +25 °C, V<sub>CC</sub> = 3.3 V, V<sub>C</sub> = 1.65 V, KV = 0x0.

Note 4: f<sub>XTAL</sub> = 114.144 MHz, Ta = +25 °C, V<sub>CC</sub> = 2.5 V, V<sub>C</sub> = 1.25 V, KV = 0x0.

Note 5: The output clock may contain spurious that depends on the settings of fo, f<sub>XTAL</sub>, PLL and output divider. The RMS jitter may be worse, if the spurious is in integration range of RMS jitter. For more information, please contact us.

**Frequency Change Time**

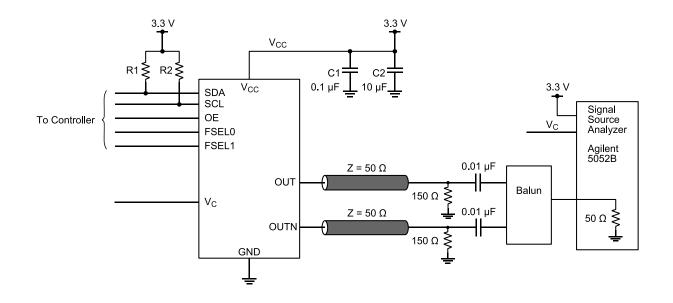

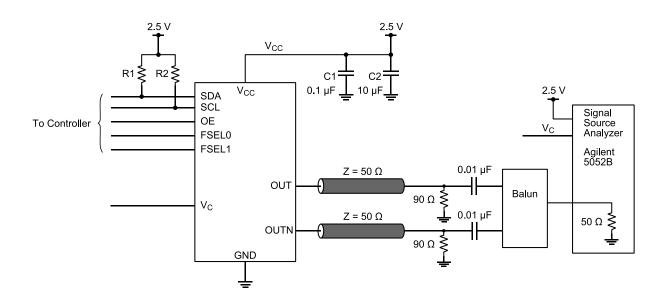

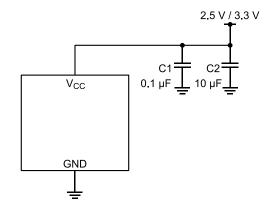

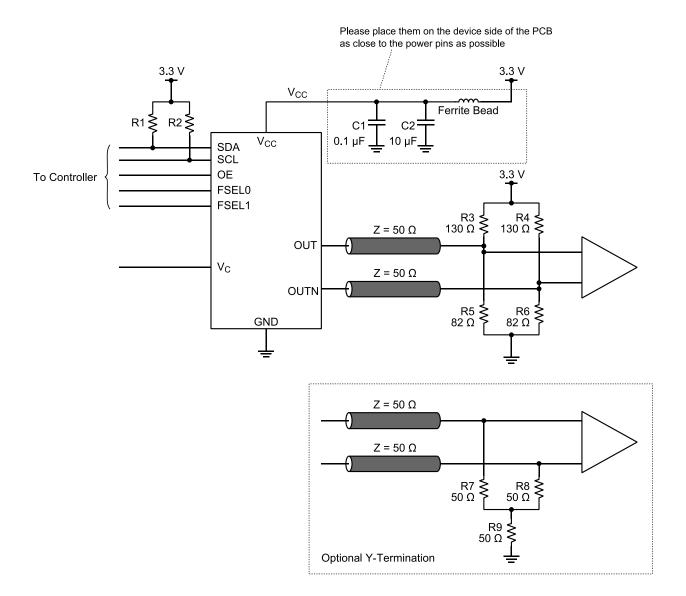

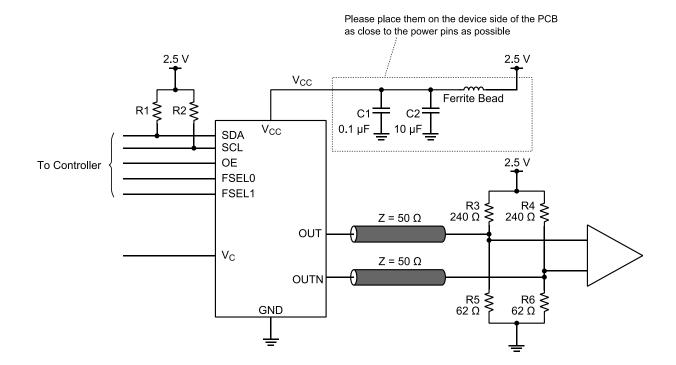

**Phase Noise Test Circuit**

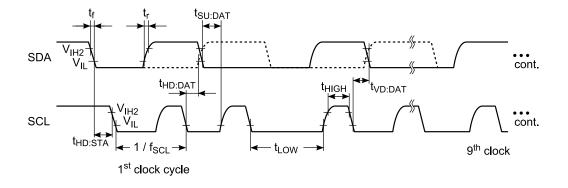

Table 5.4. Serial Interface

$V_{CC}$  = 3.3 V ± 10% or 2.5 V ± 5%, GND = 0 V, Ta = -40 ~ +85 °C

| - 00 0.0                                                                                           |                     |               | , -              | - ,        |      |       |

|----------------------------------------------------------------------------------------------------|---------------------|---------------|------------------|------------|------|-------|

| Item                                                                                               | Symbol              | Conditions    | Min.             | Тур.       | Max. | Units |

| SCL clock frequency                                                                                | f <sub>SCL</sub>    | -             | -                | -          | 400  | kHz   |

| Hold time (repeated) START condition,<br>After this period, the first clock pulse is<br>generated. | t <sub>HD;STA</sub> | 1             | 0.6              | -          | -    | μs    |

| Low period of the SCL clock                                                                        | t <sub>LOW</sub>    | -             | 1.3              | -          | -    | μs    |

| High period of the SCL clock                                                                       | t <sub>HIGH</sub>   | -             | 0.6              | -          | -    | μs    |

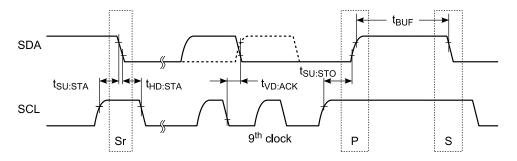

| Set up time for a repeated START condition                                                         | t <sub>SU;STA</sub> | -             | 0.6              | -          | -    | μs    |

| Input data hold time                                                                               | t <sub>HD;DAT</sub> | -             | 0                | -          | -    | μs    |

| Output data set-up time                                                                            | t <sub>SU;DAT</sub> | -             | 100              | -          | -    | ns    |

| Rise time of both SDA and SCL signals <sup>*1</sup>                                                | t <sub>r</sub>      | -             | -                | -          | 300  | ns    |

| Fall time of both SDA and SCL signals                                                              | t <sub>f</sub>      | -             | -                | -          | 300  | ns    |

| Set up time for STOP condition                                                                     | t <sub>SU;STO</sub> | -             | 0.6              | -          | -    | μs    |

| Bus free time between a STOP and START condition                                                   | t <sub>BUF</sub>    | -             | 1.3              | -          | -    | μs    |

| Data valid time                                                                                    | t <sub>VD:DAT</sub> | -             | -                | -          | 0.9  | μs    |

| Data valid acknowledge time                                                                        | t <sub>VD;ACK</sub> | -             | -                | -          | 0.9  | μs    |

| Note 1: Guaranteed by design, characterization                                                     | n, and/or sir       | nulation only | and not producti | on tested. |      | •     |

**Serial Interface**

VG7050ECN

## 5.4. VCXO Control Voltage Input (V<sub>C</sub>)

Table 5.5. VCXO Control Voltage Input (V<sub>c</sub>) Characteristics (1)

$V_{CC}$  = 3.3 V ± 10% or 2.5 V ± 5%, GND = 0 V, Ta = -40 ~ +85 °C

| Item                            | Symbol          | Conditions                    | Min. | Тур.         | Max. | Units |

|---------------------------------|-----------------|-------------------------------|------|--------------|------|-------|

| Control voltage tuning range    | Vc              | -                             | 0    | ı            | Vcc  | V     |

| V <sub>C</sub> input resistance | R <sub>IN</sub> | DC Level                      | 5    | -            | -    | МΩ    |

| Nominal Control Voltage         | $VC_{NOM}$      | V <sub>CC</sub> = 3.3 V ± 10% | -    | 1.65         | -    | V     |

|                                 |                 | V <sub>CC</sub> = 2.5 V ± 5%  | -    | 1.25         | -    |       |

| Frequency Change Polarity       |                 | -                             | P    | ositive slop | ре   | -     |

Table 5.6. VCXO Control Voltage Input (V<sub>c</sub>) Characteristics (2)

$V_{CC}$  = 3.3 V ± 10% or 2.5 V ± 5%, GND = 0 V, Ta = -40 ~ +85 °C

| Item                      | Symbol |                                                                      | Condi                                                                         | tions       | Min. | Тур. | Max | Units |

|---------------------------|--------|----------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------|------|------|-----|-------|

| Control voltage linearity | f_lin  | BSL                                                                  | BSL $V_{CC} = 3.3 \text{ V}, V_{C} = 0.3 \text{ V} \sim 3.0 \text{ V}$        |             |      | ī    | ±10 | %     |

|                           |        | $V_{CC} = 2.5 \text{ V}, V_{C} = 0.25 \text{ V} \sim 2.25 \text{ V}$ |                                                                               |             | 1    | ī    | ±10 |       |

| Modulation bandwidth      | BW     | ±3 dB, r                                                             | eference input                                                                | : 1 kHz     | 10   | -    | -   | kHz   |

| Absolute pull range *1    | APR    | $V_{CC} = 3$ .                                                       |                                                                               | KV Register |      |      |     |       |

|                           |        |                                                                      | $V_C = 0.3 \text{ V} \sim 3.0 \text{ V},$<br>$f_{XTAL} = 114.144 \text{ MHz}$ | 0x0         | ±180 | ī    | 1   | ppm   |

|                           |        | IXIAL — I                                                            | 1 1.1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                       | 0x1         | ±164 | ı    | 1   |       |

|                           |        |                                                                      |                                                                               | 0x2         | ±148 | ı    | 1   |       |

|                           |        |                                                                      |                                                                               | 0x3         | ±132 | -    | -   |       |

|                           |        |                                                                      |                                                                               | 0x4         | ±116 | -    | -   |       |

|                           |        |                                                                      |                                                                               | 0x5         | ±99  | ı    | 1   |       |

|                           |        |                                                                      |                                                                               | 0x6         | ±83  | ı    | 1   |       |

|                           |        |                                                                      |                                                                               | 0x7         | ±67  | ı    | 1   |       |

|                           |        |                                                                      |                                                                               | 0x8         | ±51  | ı    | 1   |       |

|                           |        |                                                                      |                                                                               | 0x9         | ±35  | 1    | -   |       |

|                           |        |                                                                      | 0xA                                                                           | ±19         | ı    | 1    |     |       |

|                           |        |                                                                      | 0xB                                                                           | ±3          | -    | -    |     |       |

|                           |        |                                                                      |                                                                               | KV Register |      |      |     |       |

|                           |        | .25 V ~ 2.25 V,<br>114.144 MHz                                       | 0x0                                                                           | ±183        | -    | -    | ppm |       |

|                           |        | TAIAL - I                                                            |                                                                               | 0x1         | ±166 | -    | -   |       |

|                           |        |                                                                      |                                                                               | 0x2         | ±150 | -    | -   |       |

|                           |        |                                                                      |                                                                               | 0x3         | ±134 | -    | -   |       |

|                           |        |                                                                      |                                                                               | 0x4         | ±118 | -    | -   |       |

|                           |        |                                                                      |                                                                               | 0x5         | ±102 | -    | -   |       |

|                           |        |                                                                      |                                                                               | 0x6         | ±86  | -    | -   | ]     |

|                           |        |                                                                      |                                                                               | 0x7         | ±69  | -    | ı   |       |

|                           |        |                                                                      |                                                                               | 0x8         | ±54  | -    | -   |       |

|                           |        |                                                                      |                                                                               | 0x9         | ±38  | -    | 1   |       |

|                           |        |                                                                      |                                                                               | 0xA         | ±22  | -    | 1   |       |

|                           |        |                                                                      |                                                                               | 0xB         | ±6   | -    | -   |       |

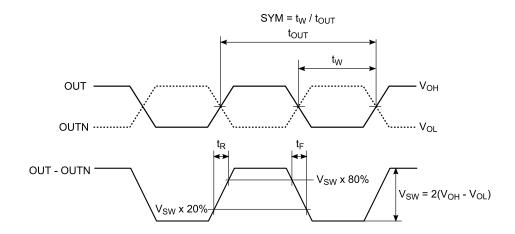

#### 5.5. LVPECL

Table 5.7. LVPECL

$V_{CC}$  = 3.3 V ± 10% or 2.5 V ± 5%, GND = 0 V, Ta = -40 ~ +85 °C

| Item                               | Symbol           | Conditions                   | Min.                                                   | Тур.                   | Max                    | Units |  |  |

|------------------------------------|------------------|------------------------------|--------------------------------------------------------|------------------------|------------------------|-------|--|--|

| Output load condition              | L_PECL           | Outputs terminated with 50 Ω | puts terminated with 50 $\Omega$ to $V_{CC}$ – 2.0 $V$ |                        |                        |       |  |  |

| Rise time <sup>*1</sup>            | t <sub>R</sub>   | -                            | -                                                      | -                      | 400                    | ps    |  |  |

| Fall time <sup>*1</sup>            | t <sub>F</sub>   | -                            | -                                                      | -                      | 400                    | ps    |  |  |

| Symmetry*1 (duty cycle)            | SYM              | -                            | 45                                                     | 50                     | 55                     | %     |  |  |

| High level output voltage          | V <sub>OH</sub>  | -                            | V <sub>CC</sub> - 1.025                                | V <sub>CC</sub> - 0.95 | -                      | V     |  |  |

| Low level output voltage           | $V_{OL}$         | -                            | -                                                      | $V_{CC} - 1.7$         | V <sub>CC</sub> – 1.62 | ٧     |  |  |

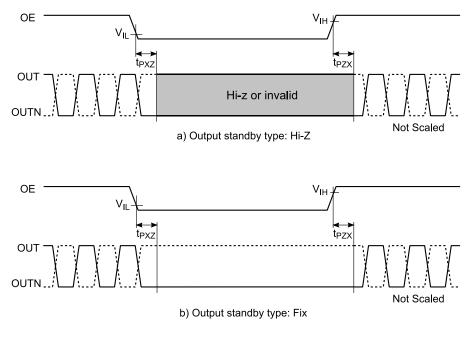

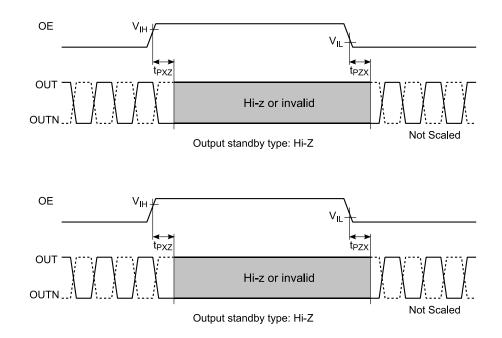

| OE disable delay time*1            | t <sub>PXZ</sub> | -                            | -                                                      | -                      | 100                    | ns    |  |  |

| OE enable delay time <sup>*1</sup> | t <sub>pZX</sub> | -                            | -                                                      | -                      | 10                     | μs    |  |  |

Note: OUT and OUTN are not used as single end.

Note 1: Guaranteed by design, characterization, and/or simulation only and not production tested.

Output Rise/Fall Time, Symmetry (duty cycle)

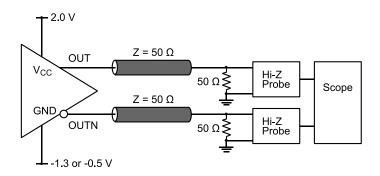

**Output AC Test Circuit**

**OE function (Active High)**

**OE function (Active Low)**

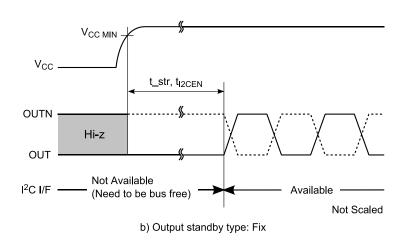

#### 5.6. Startup

Table 5.8. Startup

$V_{CC}$  = 3.3 V ± 10% or 2.5 V ± 5%, GND = 0 V, Ta = -40 ~ +85 °C

| Item                                           | Symbol             | Conditions                                        | Min.                 | Тур. | Max | Units |

|------------------------------------------------|--------------------|---------------------------------------------------|----------------------|------|-----|-------|

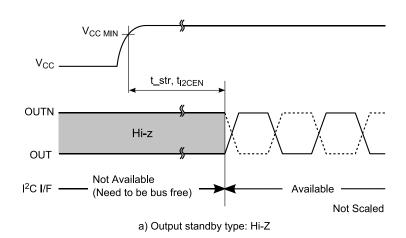

| V <sub>CC</sub> ramp rate <sup>*1</sup>        | R <sub>VCC</sub>   | V <sub>CC</sub> from 0 V to V <sub>CC MIN</sub> . | 5 x 10 <sup>-6</sup> | -    | 3   | s     |

| Startup time*2                                 | t_str              | -                                                 | -                    | -    | 5   | ms    |

| I <sup>2</sup> C I/F enable time <sup>*2</sup> | t <sub>I2CEN</sub> | -                                                 | -                    | -    | 5   | ms    |

Note 1:  $V_{\text{CC}}$  ramp must be monotonic.

Note 2: Guaranteed by design, characterization, and/or simulation only and not production tested.

**Start-Up Time**

#### 6. Functions

#### 6.1. Overview

The VG7050ECN has a VCXO, PLL and output buffer unit. The VCXO unit is composed of a fundamental mode crystal that generates stable reference clock for PLL. Kv of VCXO can be programmed via I<sup>2</sup>C interface. For best phase noise performance, Kv can be selected the lowest setting that meets the requirements of the application. The output frequency is determined by the feedback divider and the output divider. The feedback divider can offer not only integer setting that achieves lower jitter, but also fractional setting that provides frequency in ppb resolution.

The device's default output frequency and Kv are set at the factory and can be reprogrammed via I<sup>2</sup>C bus. Once the device is powered down, it will return to its factory-set default setting.

#### 6.2. Setting of the Kv

The VG7050ECN has Voltage Control function in its crystal oscillation circuit. The Kv value, pull range sensitivity of the  $V_{\mathbb{C}}$  function, is the factory default value when the device is powered on. It can be reprogrammed by setting the KV.KV register through  $I^2C$  bus.

| Register | Setting   | Kv *      |

|----------|-----------|-----------|

| KV.KV    | 0xC ~ 0xF | Forbidden |

|          | 0xB       | Min       |

|          |           |           |

|          | 0x0       | Max       |

Table 6.1. Setting of the Kv

#### 6.3. Setting of the Output Frequency

#### 6.3.1. Calculation of the Frequency Setting

The output frequency ( $f_O$ ) is determined by the VCO frequency ( $f_{VCO}$ ) and the output divider (ODIV). This is shown:

$$f_O = \frac{f_{VCO}}{ODIV} \tag{1}$$

The VCO frequency must be from 2.55 GHz to 3.20 GHz. Base on the relation between this limit and the formula (1), ODIV is calculated from the  $f_0$  as shown in Table 6.2.

The VCO frequency is determined by the reference frequency ( $f_{REF}$ ) from the VCXO and the feedback divider (N). The feedback divider (N) consists of both a 6-bit integer portion ( $N_{INT}$ ) and a 24-bit fractional portion ( $N_{FRAC}$ ) and provides the means for high-resolution frequency generation. The VCO frequency is calculated by:

$$f_{VCO} = f_{REF} \times N$$

$$= f_{REF} \times \left( N_{INT} + \frac{N_{FRAC}}{2^{24}} \right)$$

(2)

<sup>\*</sup>Please refer to the Kv values for the Table 5.6

Table 6.2. fo and ODIV

| f <sub>O</sub> [MHz] | ODIV | ODIV.ODIV register setting |

|----------------------|------|----------------------------|

| 50 ~ 57              | 56   | 0xF                        |

| 53 ~ 67              | 48   | 0xE                        |

| 64 ~ 80              | 40   | 0xD                        |

| 80 ~ 100             | 32   | 0xC                        |

| 91 ~ 114             | 28   | 0xB                        |

| 106 ~ 133            | 24   | 0xA                        |

| 128 ~ 160            | 20   | 0x9                        |

| 159 ~ 200            | 16   | 0x8                        |

| 182 ~ 229            | 14   | 0x7                        |

| 213 ~ 267            | 12   | 0x6                        |

| 255 ~ 320            | 10   | 0x5                        |

| 319 ~ 400            | 8    | 0x4                        |

| 364 ~ 457            | 7    | 0x3                        |

| 425 ~ 533            | 6    | 0x2                        |

| 510 ~ 640            | 5    | 0x1                        |

| 638 ~ 800            | 4    | 0x0                        |

The output frequency (f<sub>O</sub>) is shown:

$$f_{O} = \frac{f_{VCO}}{ODIV}$$

$$= f_{REF} \frac{\left(N_{INT} + \frac{N_{FRAC}}{2^{24}}\right)}{ODIV}$$

(3)

For example if the reference frequency ( $f_{REF}$ ) is 114.144 MHz and the output frequency is 120MHz, ODIV is fixed to "24" from the Table 6.2. The setting of N,  $N_{INT}$ ,  $N_{FRAC}$  is calculated:

$$N = N_{INT} + \frac{N_{FRAC}}{2^{24}} = \frac{f_{OUT} \times ODIV}{f_{REF}} = \frac{120.0 \times 10^6 \times 24}{114.1444444 \times 10^6} = 25.231188535690308$$

$$N_{INT} = floor(N) = floor(25.231188535690308) = 25$$

$$V_{INT} = f(00)(10) = f(00)(23.231100333070300) = 23$$

(5)

$$\begin{split} N_{FRAC} &= (N-N_{int}) \times 2^{24} = (25.231188535690308 - 25) \times 2^{24} \\ &= 0.231188535690308 \times 2^{24} \\ &\cong 3878700 = 0x3B2F2C \end{split}$$

(6)

(4)

Depending on the fo, the ODIV may become two values.

For example if the fo is 380 MHz, ODIV can be 7 or 8. Even if either of the ODIV values is selected, the same fo can be gained by setting NINT and NFRAC but phase noise included in the output signal become different. Please evaluate the performances fully in your actual usage environment and select the ODIV.

$N_{\text{FRAC}}$  is a 24-bit value. By setting 6 bit of  $N_{\text{INT}}$  and 20 bit of  $N_{\text{INT}}$  frequency resolution is 10 ppb order. The lower 4 bit of the rest of the  $N_{\text{FRAC}}$  corresponds to the setting of the frequency in 1ppb order. By setting these values, the output frequency is changed very small, but the spurious of the output signal may change significantly. Please evaluate the performances fully in your actual usage environment and fix the lower 4 bit of the  $N_{\text{FRAC}}$ .

#### 6.3.2. Reconfiguring Frequency Setting

The VG7050ECN has four sets of "user register", "user register selector" and a "PLL register". The user register stores ODIV, NINT and NFRAC. It can be reprogrammed at any time when I<sup>2</sup>C bus is available. The user resister selector is controlled by FSEL0 and FSEL1 pins. It selects one frequency settings (ODIV, NINT and NFRAC) from the four sets of user register. The PLL register is connected directly to the PLL.

When the device is powered on, the default value programmed in the non-volatile memory is automatically fetched to the four sets of user register. The user register selector selects frequency settings from them, and then it is loaded by the PLL register.

After power up, the user may change output frequency selection from the factory programmed four frequency by changing FSEL0 and FSEL1 pins. When VG7050ECN detect the change of FSEL0 and FSEL1 pins, clock output momentary stops. The, the PLL register is updated by the user register selected by FSEL0 and FSEL1 pins, PLL calibration is executed, and then clock output resumes at new frequency.

Input Frequency Select User Register FSEL<sub>0</sub> FSEL1 ODIVO, NINTO, NFRAC\_HO, NFRAC\_MO, NFRAC\_LO 0 0 Frequency 0 1 ODIV1, NINT1, NFRAC\_H1, NFRAC\_M1, NFRAC\_L1 0 Frequency 1 1 0 Frequency 2 ODIV2, NINT2, NFRAC\_H2, NFRAC\_M2, NFRAC\_L2 ODIV3, NINT3, NFRAC H3, NFRAC M3, NFRAC L3 1 1 Frequency 3

Table 6.3 Frequency selection by FSEL0 and FSEL1 pins

The user may change output frequency different than that programmed by the factory. VG7050ECN has two frequency change method, a) clock stops momently and PLL calibration, b) clock output continuously and no PLL calibration. With method "a", new output frequency can be set as any frequency. With method "b", the change of output frequency is limited within ±500 ppm.

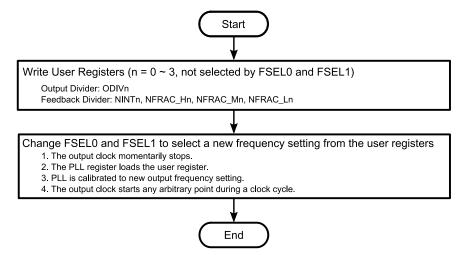

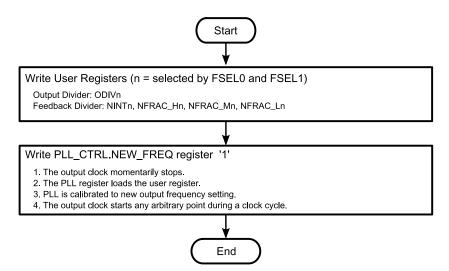

#### 6.3.2.1. Output Frequency Change to Any Frequency with PLL Calibration

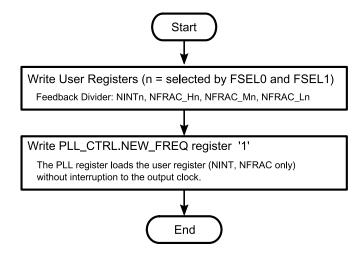

The frequency change procedure is shown in **Figure 6.1**.

If the user write a different ODIVn, NINTn, NFRAC\_Hn, NFRAC\_Mn, NFRAC\_Ln; n = 0, 1, 2 or 3, the user writes to a configuration which is not currently selected by FSEL0 and FSEL1 pins and then change to that configuration after the  $I^2C$  transaction has completed. Changing the FSEL0 and FSEL1 pins controls results in an immediate output clock halt, PLL calibration, and then output clock resumes at new frequency.

If FSEL0 and FSEL1 pins are fixed, the user writes to a configuration which is currently selected by FSEL0 and FSEL1 pins, and writes 1 to the PLL\_CTRL.NEW\_FREQ register. It also results in an immediate output clock halt, PLL calibration, and then output clock resumes at new frequency.

Both method results in PLL calibration for new output frequency, optimum jitter performance is achieved. These methods establish a new center frequency. Circuitry receiving a clock from the VG7050ECN that is sensitive to glitches or runt pulses may have to be reset once this process is complete.

a) Change a frequency setting and select it by FSEL0, FSEL1

b) Change a frequency setting and request to load it

Figure 6.1 Frequency change procedure with PLL calibration

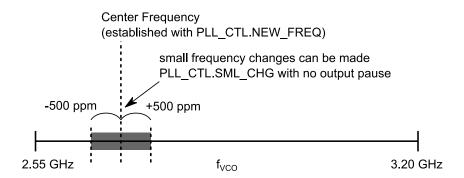

#### 6.3.2.2. Output Frequency Small Change without PLL Calibration

The user may change output frequency without clock pause. With this method, PLL calibration is not executed and frequency change window is limited within ±500 ppm from the center frequency as shown in Figure 6.2

Figure 6.2 VCO frequency range

Frequency change procedure is shown in Figure 6.3. The user may write new frequency settings to the user resister (NINT, NFRAC only) which is selected by FSEL0 and FSEL1 pins, and then the user write 1 to the PLL\_CTRL.SML\_CHG register. It results in a change of output frequency without clock output pause.

PLL calibration is not preceded in this method; therefore the jitter performance may not be optimum. During output frequency change, the output frequency might temporarily be outside the frequency band between old frequency and new frequency.

Figure 6.3 Frequency change procedure without PLL calibration

## 6.4. I<sup>2</sup>C Interface

#### 6.4.1. Connection of I<sup>2</sup>C Bus

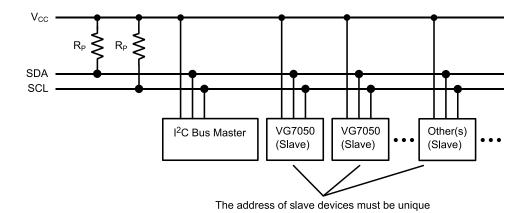

The VG7050ECN can be used as a slave device of  $I^2C$  bus. The  $I^2C$  bus is composed of serial data line (SDA) and serial clock (SCL). The lines need to be both pulled up by external resistors. Electric level of the pull up resistor need to be above the Vcc so these are recommended to be pulled up to the Vcc. Also slave address of the slave devices on the  $I^2C$  bus must be unique.

Figure 6.4. Connection of I<sup>2</sup>C bus

#### 6.4.2. I<sup>2</sup>C Bus Protocols Supported by the VG7050ECN

I2C bus protocols that can be supported by the VG7050ECN are shown in the below Table 6.4.

Table 6.4. I<sup>2</sup>C bus protocols supported by the VG7050ECN

| Feature              | VG7050ECN |

|----------------------|-----------|

| START condition      | ✓         |

| STOP condition       | ✓         |

| Acknowledge          | ✓         |

| Clock stretching     | n/a       |

| 7-bit slave address  | ✓         |

| 10-bit slave address | n/a       |

| General Call address | n/a       |

| Software Reset       | n/a       |

| Device ID            | n/a       |

n/a = not applicable

#### 6.4.3. START Condition and STOP Condition

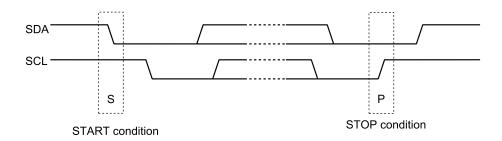

Data communication on the I<sup>2</sup>C bus starts by START condition (S). The START condition means that SDA changes from "H" to "L" when SCL is at "H". When the START condition occurs, I<sup>2</sup>C bus becomes busy.

Data communication on the  $I^2C$  bus can be terminated by STOP condition (P). The STOP condition means that SDA changes from "L" to "H" when SCL is at "H". When the STOP condition occurs,  $I^2C$  bus becomes free.

When  $I^2C$  bus is busy, instead of STOP condition START condition can be generated, which is called repeated START condition (Sr). The  $I^2C$  bus maintains busy status. If the START or repeated START condition is received,  $I^2C$  interface circuit of the VG7050ECN is always reset, even if these START conditions are not positioned according to the proper format.

Figure 6.5. START and STOP condition

#### 6.4.4. Byte Format and ACK/NACK

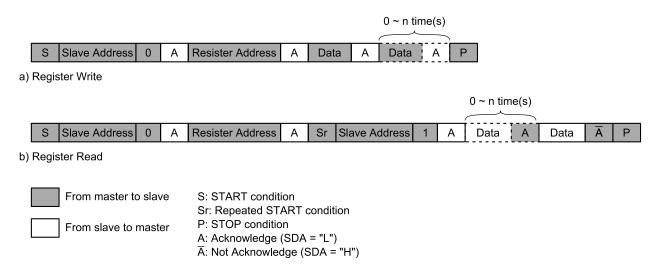

Data transmission and reception on  $I^2C$  is done in a unit of 8 bit = 1 byte. Each byte is followed by acknowledge bit. Data is transmitted by MSB first. Including acknowledge bit all SCL pulses are generated by Master.

The Acknowledge signal (ACK: A) is defined as follows: the transmitter (master transmitter or slave transmitter) releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line "L" and it remains stable "L" during the "H" period of this clock pulse. When SDA remains "H" during this ninth clock pulse, this is defined as the Not Acknowledge signal (NACK:  $\overline{A}$ ).

#### 6.4.5. Read/Write to Register

Procedure of Read/Write to register is shown in the below Figure 6.6. The VG7050ECN can Read/Write single or multi byte data. The VG7050ECN slave address is able to be specified by the customer. It will be programmed to non-volatile memory at our factory.

Figure 6.6. Read/Write from/to register by I<sup>2</sup>C bus

**EPSON**

# 7. Registers

# 7.1. List of Registers

| A -1-1  | Register   |         |                             |      | Е              | Bit             |              |           |                 |  |

|---------|------------|---------|-----------------------------|------|----------------|-----------------|--------------|-----------|-----------------|--|

| Address | name       | Bit7    | Bit6                        | Bit5 | Bit4           | Bit3            | Bit2         | Bit1      | Bit0            |  |

| 0x00    | P_CODE0    |         | 0x46 (Ascii 'F', Read Only) |      |                |                 |              |           |                 |  |

| 0x01    | P_CODE1    |         |                             | (    | 0x43 (Ascii 'C | C', Read Only   | )            |           |                 |  |

| 0x02    | REV        |         |                             |      | 0x01 (Re       | ead Only)       |              |           |                 |  |

| 0x03    | ID_CODE0   |         |                             |      | 0x01 (Re       | ead Only)       |              |           |                 |  |

| 0x04    | ID_CODE1   | -       |                             |      |                | D (Read Only    | <u>'</u> )   |           |                 |  |

| 0x10    | ODIV0      | -       | -                           | -    | -              |                 | 10           | DIV       |                 |  |

| 0x11    | NINT0      | -       | -                           |      |                | NII             | NT           |           |                 |  |

| 0x12    | NFRAC_H0   |         |                             |      | NFR            | AC_H            |              |           |                 |  |

| 0x13    | NFRAC_M0   |         |                             |      | NFR            | AC_M            |              |           |                 |  |

| 0x14    | NFRAC_L0   |         |                             |      | NFR            | AC_L            |              |           |                 |  |

| 0x15    | PLL_CTRL0  | OE_REG  | 1                           | -    | -              | VCTUNE_D<br>IS  | NEW_FRE<br>Q | SML_CHG   | NVM_RES<br>TORE |  |

| 0x16    | FSEL_STAT0 | -       | -                           | -    | -              | FSEL (Read Only |              | ead Only) |                 |  |

| 0x20    | ODIV1      | -       | ODIV                        |      |                |                 |              |           |                 |  |

| 0x21    | NINT1      | -       | NINT                        |      |                |                 |              |           |                 |  |

| 0x22    | NFRAC_H1   |         | NFRAC_H                     |      |                |                 |              |           |                 |  |

| 0x23    | NFRAC_M1   |         |                             |      | NFR            | AC_M            |              |           |                 |  |

| 0x24    | NFRAC_L1   |         |                             |      | NFR.           | AC_L            |              |           |                 |  |

| 0x30    | ODIV2      | -       | -                           | -    | -              |                 | 00           | DIV       |                 |  |

| 0x31    | NINT2      | -       | -                           |      |                | NII             | NT           |           |                 |  |

| 0x32    | NFRAC_H2   |         |                             |      | NFR            | AC_H            |              |           |                 |  |

| 0x33    | NFRAC_M2   |         |                             |      | NFR            | AC_M            |              |           |                 |  |

| 0x34    | NFRAC_L2   |         |                             |      | NFR.           | AC_L            |              |           |                 |  |

| 0x40    | ODIV3      | -       | -                           | -    | -              |                 | 00           | OIV       |                 |  |

| 0x41    | NINT3      | -       | - NINT                      |      |                |                 |              |           |                 |  |

| 0x42    | NFRAC_H3   | NFRAC_H |                             |      |                |                 |              |           |                 |  |

| 0x43    | NFRAC_M3   | NFRAC_M |                             |      |                |                 |              |           |                 |  |

| 0x44    | NFRAC_L3   |         | NFRAC_L                     |      |                |                 |              |           |                 |  |

| 0x50    | PLL_CTRL1  | OE_REG  | -                           | -    | -              | VCTUNE_D<br>IS  | NEW_FRE<br>Q | SML_CHG   | NVM_RES<br>TORE |  |

| 0x51    | FSEL_STAT1 | -       | -                           | -    | -              | -               | -            | FSEL (R   | ead Only)       |  |

| 0x5A    | KV         | -       |                             |      |                |                 |              |           |                 |  |

Note: Please do not write values in the addresses that are not mentioned in this list. Please write 0 in the bit that is not defined.

# 7.2. Product Code 0 Register

| Address Register |         |      |        |      | В    | Bit  |      |      |      |

|------------------|---------|------|--------|------|------|------|------|------|------|

| Address          | name    | Bit7 | Bit6   | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 0x00             | P_CODE0 |      | P_CODE |      |      |      |      |      |      |

| Туре             |         |      |        |      | R    | /O   |      |      |      |

| Default          |         | 0    | 1      | 0    | 0    | 0    | 1    | 1    | 0    |

| Bit | Name   | Function                           |

|-----|--------|------------------------------------|

| 7:0 | P_CODE | Product code (0x46) Ascii Code 'F' |

## 7.3. Product Code 1 Register

| Address | Register |      |        |      | В    | Bit  |      |      |      |

|---------|----------|------|--------|------|------|------|------|------|------|

| Address | name     | Bit7 | Bit6   | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 0x01    | P_CODE1  |      | P_CODE |      |      |      |      |      |      |

| Туре    |          |      |        |      | R    | /O   |      |      |      |

| Default |          | 0    | 1      | 0    | 0    | 0    | 0    | 1    | 1    |

| I | Bit | Name   | Function                           |

|---|-----|--------|------------------------------------|

|   | 7:0 | P_CODE | Product code (0x43) Ascii Code 'C' |

# 7.4. Revision Code Register

| Address | Register |      |      |      | В    | Bit  |      |      |      |

|---------|----------|------|------|------|------|------|------|------|------|

| Address | name     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 0x02    | REV      |      | REV  |      |      |      |      |      |      |

| Туре    |          |      |      |      | R    | /O   |      |      |      |

| Default |          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |

|   | Bit | Name | Function              |

|---|-----|------|-----------------------|

| ſ | 7:0 | REV  | Revision code<br>0x01 |

# 7.5. ID Code 0 Register

| Address | Register |      |      |      | В    | Bit  |      |      |      |

|---------|----------|------|------|------|------|------|------|------|------|

| Address | name     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 0x03    | ID_CODE0 |      | ID   |      |      |      |      |      |      |

| Туре    |          |      |      |      | R    | /O   |      |      |      |

| Default |          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |

| Bit | Name | Function        |

|-----|------|-----------------|

| 7:0 | ID   | ID code<br>0x01 |

# 7.6. ID Code 1 Register

| A dalmaga | Register | Bit  |      |      |      |             |        |      |      |  |  |

|-----------|----------|------|------|------|------|-------------|--------|------|------|--|--|

| Address   | name     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3        | Bit2   | Bit1 | Bit0 |  |  |

| 0x04      | ID_CODE1 | -    |      | ID   |      |             |        |      |      |  |  |

| -         | Туре     |      | R/O  |      |      |             |        |      |      |  |  |

| Default   |          | -    |      |      | Depe | nd on the p | roduct |      |      |  |  |

| Bit | Name     | Function                                                         |  |  |  |  |  |

|-----|----------|------------------------------------------------------------------|--|--|--|--|--|

| 7   | Reserved | Always read as 0.                                                |  |  |  |  |  |

| 6:0 | ID       | ID code Lower 7 bit value of the parameter designator (SM20xxxx) |  |  |  |  |  |

# 7.7. ODIV Register

| Address | Register | Bit  |      |      |      |       |      |      |      |  |  |  |

|---------|----------|------|------|------|------|-------|------|------|------|--|--|--|

| Address | name     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3  | Bit2 | Bit1 | Bit0 |  |  |  |

| 0x10    | ODIV0    |      |      |      |      |       |      |      |      |  |  |  |

| 0x20    | ODIV1    |      |      |      | _    |       | ODIV |      |      |  |  |  |

| 0x30    | ODIV2    | -    | -    | -    | -    |       |      |      |      |  |  |  |

| 0x40    | ODIV3    |      |      |      |      |       |      |      |      |  |  |  |

|         | Туре     | ı    | ı    | ı    | ı    | - R/W |      |      |      |  |  |  |

|         | efault   | 1    | -    | ı    | 1    | NVM   |      |      |      |  |  |  |

| Bit | Name     | Function                             |                                         |                                          |                                          |  |  |  |  |

|-----|----------|--------------------------------------|-----------------------------------------|------------------------------------------|------------------------------------------|--|--|--|--|

| 7:4 | Reserved | Please write 0 at                    | Please write 0 at all the times.        |                                          |                                          |  |  |  |  |

| 3:0 | ODIV     | 0x0: 4<br>0x1: 5<br>0x2: 6<br>0x3: 7 | 0x4: 8<br>0x5: 10<br>0x6: 12<br>0x7: 14 | 0x8: 16<br>0x9: 20<br>0xA: 24<br>0xB: 28 | 0xC: 32<br>0xD: 40<br>0xE: 48<br>0xF: 56 |  |  |  |  |

# 7.8. NINT Register

| A alalua a a | Register |      | Bit  |      |      |      |      |      |      |  |  |

|--------------|----------|------|------|------|------|------|------|------|------|--|--|

| Address      | name     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

| 0x11         | NINT0    |      |      |      |      |      |      |      |      |  |  |

| 0x21         | NINT1    |      |      |      |      | NUNT |      |      |      |  |  |

| 0x31         | NINT2    | -    | -    | NINT |      |      |      |      |      |  |  |

| 0x41         | NINT3    |      |      |      |      |      |      |      |      |  |  |

| Type         |          | -    | -    | R/W  |      |      |      |      |      |  |  |

| Default      |          | -    | -    | NVM  |      |      |      |      |      |  |  |

| Bit | Name     |                               | Function                                                   |                                       |  |  |  |  |  |

|-----|----------|-------------------------------|------------------------------------------------------------|---------------------------------------|--|--|--|--|--|

| 7:6 | Reserved | Please write 0 at all th      | e times.                                                   |                                       |  |  |  |  |  |

| 5:0 | NINT     | Integer portion of the        | nteger portion of the feedback divider (N <sub>INT</sub> ) |                                       |  |  |  |  |  |

|     |          | Set                           | Setting Description                                        |                                       |  |  |  |  |  |

|     |          | 0x00 ~ 0x11,                  | 0d ~ 17d                                                   | This setting shall not be configured. |  |  |  |  |  |

|     |          | 0x12                          | 18d                                                        | N <sub>INT</sub> = 18                 |  |  |  |  |  |

|     |          |                               |                                                            |                                       |  |  |  |  |  |

|     |          | $0x20$   32d   $N_{INT} = 32$ |                                                            |                                       |  |  |  |  |  |

|     |          | 0x21 ~ 0x3F                   | 33d ~ 63d                                                  | This setting shall not be configured. |  |  |  |  |  |

# 7.9. NFRAC Register

| A ddrago | Register |      |              |      | E     | it      |      |      |      |  |

|----------|----------|------|--------------|------|-------|---------|------|------|------|--|

| Address  | Name     | Bit7 | Bit6         | Bit5 | Bit4  | Bit3    | Bit2 | Bit1 | Bit0 |  |

| 0x12     | NFRAC_H0 |      |              |      |       |         |      |      |      |  |

| 0x22     | NFRAC_H1 |      |              |      | NEDAC | 100.461 |      |      |      |  |

| 0x32     | NFRAC_H2 |      | NFRAC[23:16] |      |       |         |      |      |      |  |

| 0x42     | NFRAC_H3 |      |              |      |       |         |      |      |      |  |

| 0x13     | NFRAC_M0 |      |              |      |       |         |      |      |      |  |

| 0x23     | NFRAC_M1 |      | NFRAC[15:8]  |      |       |         |      |      |      |  |

| 0x33     | NFRAC_M2 |      |              |      | NEIXA | J[13.0] |      |      |      |  |

| 0x43     | NFRAC_M3 |      |              |      |       |         |      |      |      |  |

| 0x14     | NFRAC_L0 |      |              |      |       |         |      |      |      |  |

| 0x24     | NFRAC_L1 |      |              |      | NEDA  | C[7:0]  |      |      |      |  |

| 0x34     | NFRAC_L2 |      |              |      | NEINA | .0[7.0] |      |      |      |  |

| 0x44     | NFRAC_L3 |      |              |      |       |         |      |      |      |  |

|          | Туре     | R/W  |              |      |       |         |      |      |      |  |

|          | efault   |      |              |      | N\    | /M      | •    | •    |      |  |

| Bit | Name                                      | Function                                                                                                                                                            |

|-----|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | NFRAC[23:16]<br>NFRAC[15:8]<br>NFRAC[7:0] | Fractional portion of the feedback divider (N <sub>FRAC</sub> )  E.g. Setting in case N <sub>FRAC</sub> is 0x123456  NFRAC_H = 0x12  NFRAC_M = 0x34  NFRAC_L = 0x56 |

# 7.10. PLL Control Register

| Address      | Register               |        | Bit  |      |      |                |              |             |                 |  |  |  |

|--------------|------------------------|--------|------|------|------|----------------|--------------|-------------|-----------------|--|--|--|

| Address      | name                   | Bit7   | Bit6 | Bit5 | Bit4 | Bit3           | Bit2         | Bit1        | Bit0            |  |  |  |

| 0x15<br>0x50 | PLL_CTRL0<br>PLL_CTRL1 | OE_REG | -    | -    | -    | VCTUNE_<br>DIS | NEW_FR<br>EQ | SML_CH<br>G | NVM_RE<br>STORE |  |  |  |

|              | Туре                   | R/W    | -    | -    | -    | R/W            | R/W          | R/W         | R/W             |  |  |  |

| Default      |                        | 0      | -    | -    | -    | 0              | 0            | 0           | 0               |  |  |  |

PLL\_CTRL0 and PLL\_CTRL1 is an address shared register.

| Bit | Name        |                                                     |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                      | Function                                                       |                                                                   |                                        |  |  |  |

|-----|-------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------|--|--|--|

| 7   | OE_REG      |                                                     | Output enable register function  LVPECL output buffer is enable when OE pin or this register is set as 1/High as shown below table.                                                                                                                                                                                                                     |                                                                                                      |                                                                |                                                                   |                                        |  |  |  |

|     |             |                                                     |                                                                                                                                                                                                                                                                                                                                                         | LVF                                                                                                  | PECL output buff                                               | er                                                                |                                        |  |  |  |